SAR ADC的隔离( 二 )

文章图片

文章图片

图6.LT3999及其与同步引脚的切换关系

图5显示了变压器处的电流波形(初级侧和次级侧电流) , 它更好地利用了变压器 , 提供更好的EMI行为 。

图6显示了与外部时钟信号的同步 。采集阶段的末端与同步引脚的正边沿对齐 。因此 , 将有一个大约4μs的较长安静时间 。这使得转换器可以在该时间范围内对输入信号进行采样 , 并将隔离电源的瞬变效应降至最小 。LTC2378-20的采集时间为312 ns , 非常适合数据隔离

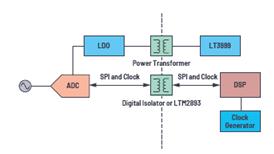

数据隔离可以使用数字隔离器实现 , 例如ADuMx系列数字隔离器 。这些数字隔离器可用于SPI、I2C、CAN等许多标准接口 , 例如ADuM140 可用于SPI隔离 。为了实现数据隔离 , 只需将SPI信号SPI时钟、SDO、SCK和Busy连接到数据隔离器 。在数据隔离中 , 电能通过感性隔离栅从初级侧传输到次级侧 。需要添加电流返回路径 , 这由电容来完成 。该电容可以在PCB中利用重叠平面实现 。

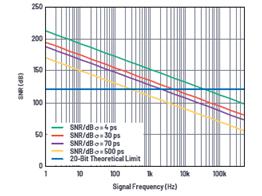

时钟隔离

时钟隔离是另一项重要任务 。如果使用1 MHz采样速率的20位高性能ADC , 例如LTC2378-20 , 可以实现104 dB的信噪比(SNR) 。为了实现高性能 , 需要无抖动时钟 。为什么不应使用像ADuM14x系列这样的标准隔离器?标准隔离器会增加时钟抖动 , 从而限制ADC的性能 。更多详细信息请参见设计笔记DN1013 。

图7显示了不同频率、不同类型时钟抖动下SNR的理论极限 。像LTC2378这样的高性能ADC的孔径时钟抖动为4 ps , 在200 kHz输入下理论限值为106 dB 。

文章图片

文章图片

图7.时钟抖动与ADC性能的关系

文章图片

文章图片

图8.使用标准隔离器实现时钟隔离

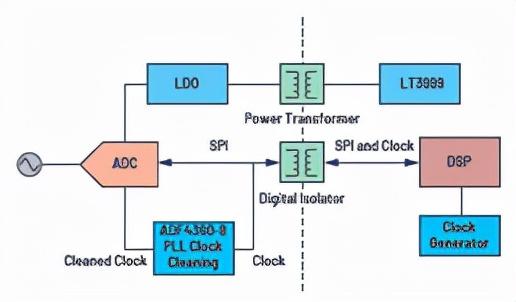

图8显示的标准时钟隔离器概念包括:

像ADuM250N这样良好的标准数字隔离器的抖动为70 ps rms 。对于100 dB SNR目标 , 由于时钟抖动 , 信号采样速率限制为20 kHz 。

像LTM2893这样优化的时钟隔离器提供30 ps rms的低抖动 。对于100 dB SNR目标 , 现在的信号采样速率为50 kHz , 在全部SNR性能下可提供更多带宽 。

文章图片

文章图片

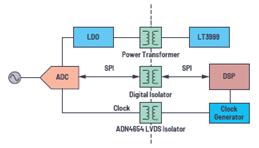

图9.使用LVDS时钟隔离器实现时钟隔离

图9:对于更高的输入频率 , 应使用LVDS隔离器 。ADN4654提供2.6 ps抖动 , 接近ADC的最佳性能 。在100 kHz输入时 , 时钟抖动导致的SNR限值将是110 dB 。

文章图片

文章图片

图10.使用额外PLL净化时钟抖动的时钟隔离

图10:使用PLL净化时钟 。ADF4360-9可以帮助减少时钟抖动 。

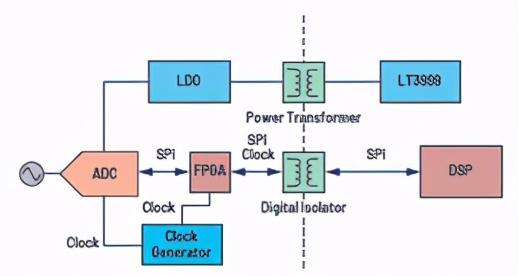

图11显示了使用PLL净化时钟的更详细框图 。您可以将ADF4360-9用作时钟净化器 , 并在输出端增加一个2分频器 。AD7760额定支持1.1 MHz 。

文章图片

文章图片

图11.ADF4360-9用作时钟净化器

因此 , 不能直接支持LTC2378等1 MSPS SAR ADC 。在这种情况下 , 低抖动触发器会有帮助 。它将时钟2分频 。

文章图片

文章图片

图12.触发器用于降低时钟以用于LTC2378

- 智库论坛 | 社区电商推动供应链数字化转型的对策建议

- 人类与AI如何共处?诺奖科学家、将棋天才、“低欲望社会”提出者的不同解答

- 线上新书发布!云上带你了解有关“冬奥”的那些事儿

- 我的世界大闹天宫龙宫怎么玩(我的世界大闹天宫龙宫打法技巧一览)

- 复苏的魔女竞技场用什么队伍(复苏的魔女竞技场队伍搭配心得分享)

- 复苏的魔女魔导装备boss怎么打(复苏的魔女魔导妨害装备获取攻略大全)

- 今年的iphonese,还是你熟悉的模样

- 长安福特蒙迪欧在中国市场的“全球化”

- safari浏览器中的indexeddb漏洞

- 复苏的魔女时空裂隙用什么阵容好(复苏的魔女时空裂隙阵容搭配指南)