高通被人骂了两年火龙,到底是谁的锅?( 二 )

缝缝补补来硬抗这漏电问题 。

文章图片

文章图片

>/到底是工艺不行么?

那既然大家都是硬抗这漏电 , 那为啥隔壁人家隔壁苹果就可以把能耗比控制的那么好?

这就不得不提广为人知的第一个背锅侠了:

文章图片

文章图片

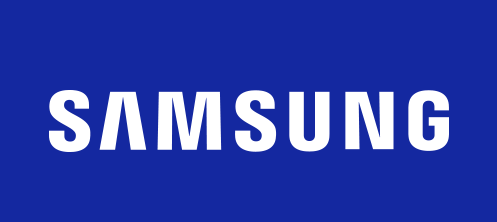

和苹果不同 , 高通这两代的SoC都是找三星代工生产 。

别看三星 , 台积电啊都称呼自己的技术叫5nm 。

但是在如今FinFET的时代 , 工艺的名称和芯片的物理参数其实并没有直接对应 , 更像是一种技术节点的称呼 。

这两家5nm工艺做出来的晶体管密度差距 , 里面甚至还能塞下一个英特尔的14nm 。

单从晶体管密度来说 , 台积电的5nm工艺可以做到在每立方毫米里摆下1713万个晶体管 , 也就是171.3MTR 。

文章图片

文章图片

而三星的5nm却只能做到126.5MTR的水平 。

在这里我提一点额外的小知识 , 之所以在晶体管密度上有这些差别 , 这和两家厂商的技术迭代路线有关 。

文章图片

文章图片

我们长话短说 , 对台积电来讲 , 我们可以理解成台积电的7nm->5nm是一次完整的技术迭代路线 。

另一边的三星则是激进了许多 , 在他们的计划中 , 可能7nm->3nm才是一次完整的技术迭代 , 他们打算首发直接在3nm工艺上全新的GAA 。

所以对于三星来讲 , 它的5nm工艺相比自家的7nm进步就略显保守 。

不过说实话 , 从单个晶体管的角度来讲 , 这点差距其实也还好 。

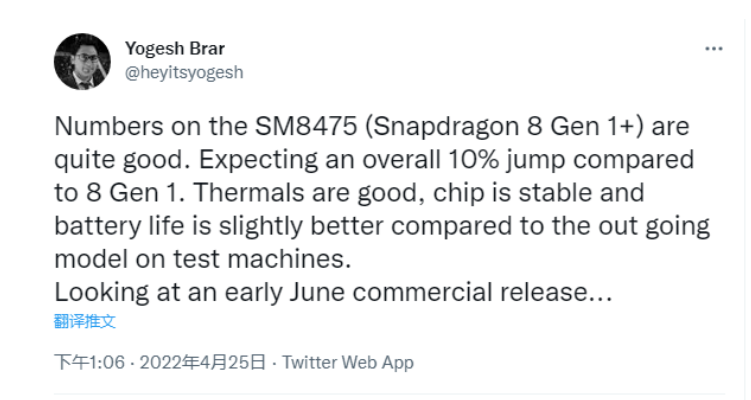

还有人认为三星工艺的良品率也值得说道说道 。

前俩月 , 一个新闻把托尼给看笑了 。。。

文章图片

文章图片

不是 , 你良品率为啥低 , 你居然自己心里没数???

根据@wccftech报道 , 三星晶圆代工部门在4nm制程上的良品率只有35%的水平 。

而还在研发中的三星3nmGAA技术良品率更是仅仅10%~20%的水平 。

文章图片

文章图片

根据DigiTimes报道 , 三星在5nm、4nm、3nm工艺上都存在着良品率谎报的情况 。

咱甚至不清楚 , 现在这个良品率是谎报前 , 还是谎报后的数字 。

也不知道是不是这个原因 , 吓得高通决定把4nm的8Gen1plus来交给台积电来代工 。

文章图片

文章图片

哦对了 , 那么隔壁台积电的4nm工艺良品率是多少呢?

70% 。。

当然了 , 我们在这儿分析工艺和密度差距 , 只能说算是在旁敲侧击的推理三星和台积电工艺的差距 。

但是在托尼看来 , 这次发热的“黑锅” , 可不能全丢给三星的代工 。

>/还是架构顶不住?

为什么托尼觉得全都怪三星是不对的呢?

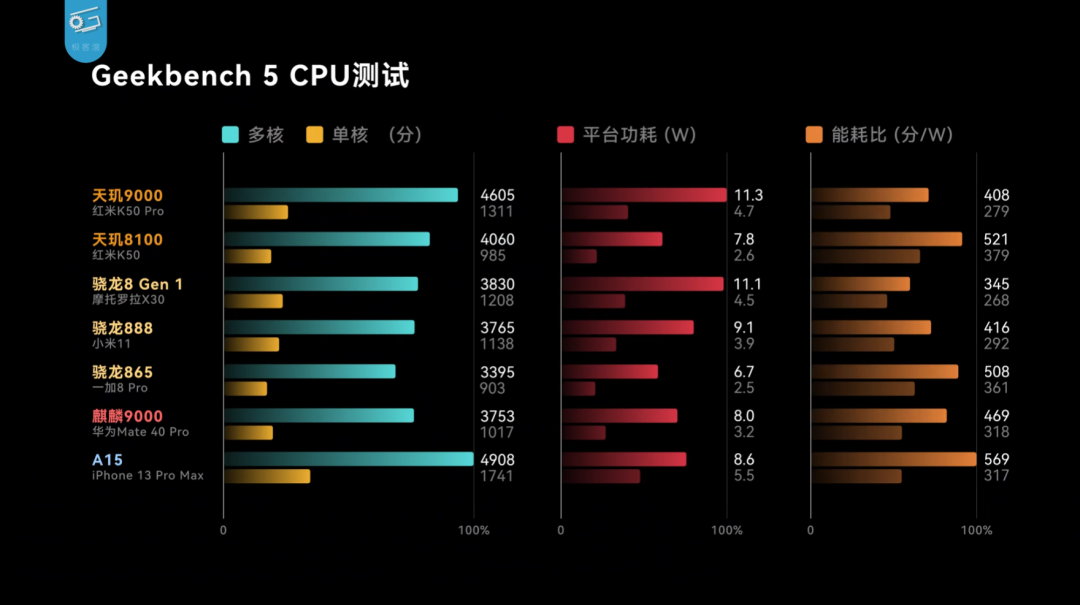

因为天玑9000来了 。

曾经被我们寄予厚望 , 交给台积电代工的天玑9000 , 功耗也不是非常理想 。

数据来源 , 极客湾▼

- 高通骁龙8plus即将发布,新体验有啥变化?

- amd、高通宣布跨界合作:锐龙6000pro系列连接系统

- 高通取代verizon进入三星电子五大客户行列

- 高通骁龙8plus旗舰处理器5月20日发布

- 高通官宣:骁龙8plus将于5月20日发布

- vivos15首发搭载高通骁龙870巅峰版

- 高通最长寿的骁龙8系!骁龙870火了一年多热度依旧不减

- 十年前被Linux之父骂 比AMD晚六年 英伟达终于开源GP

- 骁龙x65到骁龙x70:高通解锁5g性能新体验

- 中兴axon40系列搭载高通骁龙8