台积电推出n2制造技术,芯片密度提高约1.1倍

文章图片

文章图片

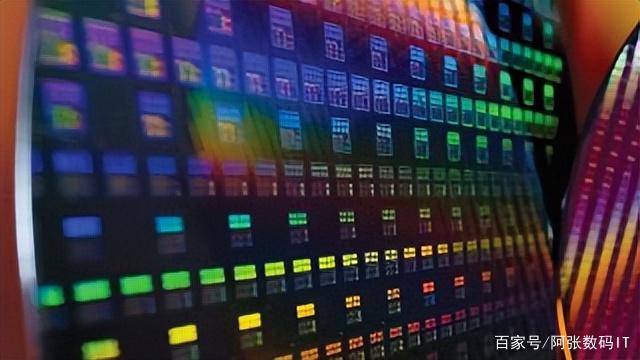

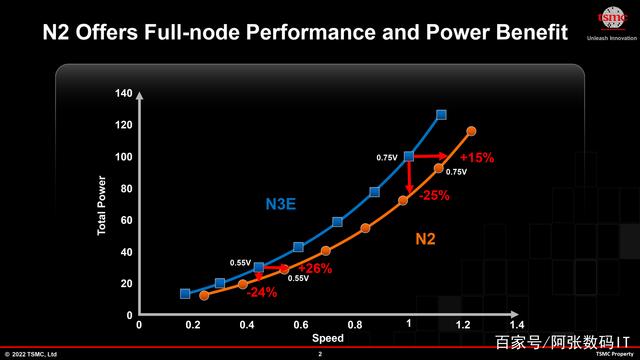

台湾积体电路制造公司今天在2022年台积电技术研讨会上正式推出了其N2(2nm级)制造技术 , 这是其首个将使用栅极全能场效应晶体管(GAAFET)的节点 。新的制造工艺将提供全面的性能和功率优势 , 但当涉及到晶体管密度时 , 它在2025年上线时几乎不会给人留下深刻的印象 。

作为一个全新的工艺技术平台 , 台积电的N2带来了两项重要的创新:纳米片晶体管(台积电称之为GAAFET)和背面电源轨 , 它们都服务于提高节点每瓦性能特性的相同目标 。GAA纳米片晶体管具有四面被栅极包围的通道 , 这减少了泄漏;此外 , 可以加宽其通道以增加驱动电流并提高性能 , 或缩小以最大限度地降低功耗和成本 。为了给这些纳米片晶体管提供足够的功率 , 现在浪费任何功率 , 台积电的N2使用背面功率传输 , 代工厂认为这是对抗后端(BEOL)电阻的最佳解决方案之一 。

文章图片

文章图片

事实上 , 在性能和功耗方面 , 台积电基于纳米片的N2节点在相同的功耗和复杂性下的性能可以提高10%至15% , 与台积电的N3E相比 , 在相同的频率和晶体管数量下功耗可降低25%至30% 。然而 , 与N3E相比 , 新节点仅将芯片密度提高了约1.1倍 。

文章图片

文章图片

一般来说 , 台积电的N3确实提供了全节点性能提升和功耗降低 。但在密度方面 , 新技术很难给人留下深刻的印象 。例如 , 台积电的N3E节点提供比N5高出1.3倍的芯片密度 , 这是一个实质性的提升 。为了公正起见 , 我们需要注意的是 , 台积电在其2022年技术研讨会上发表的材料中使用了一些复杂的“芯片密度”指标来描述N3E和N2上的晶体管密度 。芯片密度基本上描述了由50%逻辑 , 30%SRAM和20%模拟电路组成的假设芯片 。现代设计非常注重SRAM , 但SRAM几乎无法扩展 , 就像模拟电路一样 。因此 , 与N3EIC相比 , 具有50%不缩放电路的N2芯片将表现出平庸的可扩展性 。如果与N3S(N3的晶体管密度优化版本)相比 , 结果可能更不令人印象深刻 。

台积电将其N2定位为各种应用 , 包括移动SoC , 高性能CPU和GPU 。在N2平台的功能中(除了GAA纳米片晶体管和背面电源轨之外) , 世界排名第一的代工厂提到了“小芯片集成” , 这可能意味着许多将使用N2的应用也将使用多小芯片封装来优化性能和成本 。

文章图片

文章图片

【台积电推出n2制造技术,芯片密度提高约1.1倍】据报道 , 台积电将在2025年下半年开始使用其N2节点大批量生产芯片 , 因此考虑到当代半导体生产周期有多长 , 预计商用2nm芯片将在2025年底或2026年上市 。当然 , 在此之前和2026年 , 台积电将提供各种N3(3nm级)节点 , 但这是另一回事 。

- 台积电计划在2023年将其价格上涨6%

- 中国电科董事长:机器人发展要融合创新、产用互促、协同共建

- 有优惠!广西启动品质家电消费季跨界联合促销

- 潮尚、智购、夜娱……2022广西品质家电消费季跨界联动,精彩抢先看

- 英雄联盟电竞经理gala怎么出装(gala装备选择推荐)

- 只需这样操作,分分钟拦截境外骚扰电话!

- 五五购物节 | 崇明“线上嗨购”电商消费节来了!大量福利向你来

- 武汉星起航:搭乘跨境电商b2b亚马逊企业购,和世界500强做

- 多重叠加优惠来袭!8月下旬广西将开展家电消费季跨界联合促销活动

- 让设备管理更智能 国网吴忠供电公司推行“数字化掌上运检”