英特尔的多芯片封装技术是如何做到的?

【英特尔的多芯片封装技术是如何做到的?】我们都知道7nm芯片的性能比10nm强 , 4nm芯片又可以秒7nm , 谁都希望推出基于更先进制程技术生产的芯片 , 但迄今为止具备自研先进工艺芯片的厂商又有几家?

以X86为例 , 只有英特尔、AMD、兆芯等几个玩家 , 在ARM架构的手机SoC领域 , 也不过高通、联发科、三星、海思、展锐等 。更多的企业 , 只具备自研外围电路的设计实力 , 比如OPPO的马里亚纳MariSiliconXNPU、小米的澎湃C1ISP、澎湃P1智能充电芯片等 。

文章图片

文章图片

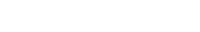

原因也很简单 , 成本太高了 。

据悉 , 如今设计一颗10nm芯片成本为1.744亿美元 , 7nm芯片约2.978亿美元 , 5nm芯片更是飙升到5.422亿美元 。

文章图片

文章图片

这个价格应该指的是SoC级别的芯片 , 但哪怕是外围芯片 , 工艺越先进所需的成本也会大幅提升也是肯定的 。

这意味着 , 传统单一工艺、单一芯片做法的难度和成本已经超过了绝大多数企业的承受能力 。

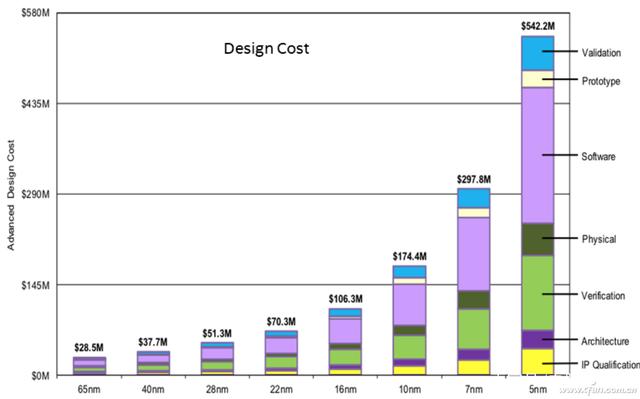

实际上 , 像英特尔和AMD这类巨头很早就意识到了这个问题 , 所以才会推出不同工艺的多芯片封装技术 , 比如英特尔移动酷睿处理器基板上 , CPU(包括核显)部分是最先进工艺 , PCH芯片则是落后一些的工艺 , 这在行业内又称为MCM(MCM-MultichipModule , 多芯片模块)2D封装技术 。

文章图片

文章图片

英特尔旗下的EMIB和台积电CoWoS则属于2.5D封装技术 , 通过它可以将7nm工艺的CPU、10nm的GPU、14nm的I/O单元、22nm的通讯单元等堆在一个基板上 。

文章图片

文章图片

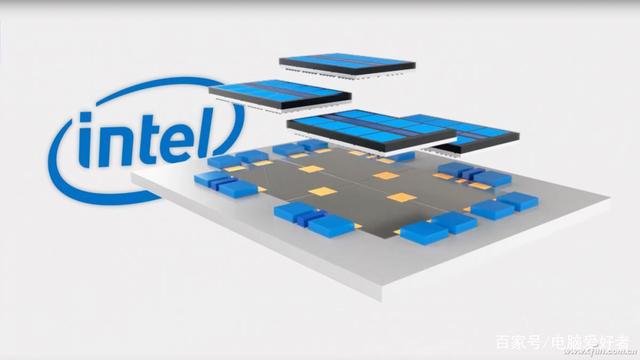

现在最先进的封装技术当属英特尔的Foveros3D封装技术 。英特尔曾在第10代酷睿时期推出过代号为“Lakefield”的混合酷睿平台——酷睿i3-L13G4和i5-L16G7这两颗处理器就首发英特尔Foveros3D封装技术和混合CPU架构(IntelHybridTechnology) , 采用了类似ARMbig.LITTLE大小核技术 , 内置1+4大小核组成的5核心 。

文章图片

文章图片

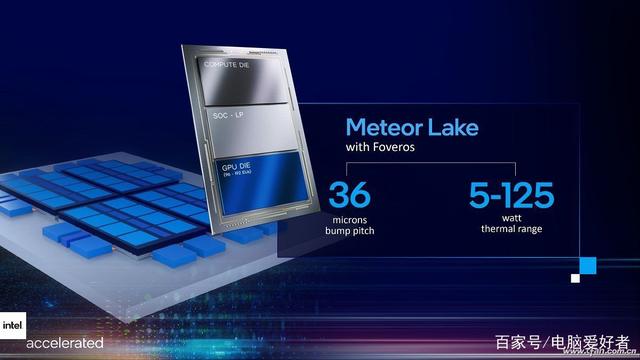

将于2023年问世的第14代酷睿MeteorLake平台 , 不仅会采用混合CPU架构技术 , 还会引入英特尔第二代Foveros3D封装技术 。它会在同一个基板上封装三个模块 , 分别是高性能计算模块、SoC-LP模块(负责I/O)和GPU模块 , 视CPU和GPU核心规模和主频 , 其TDP可在5W~125W之间浮动 。

文章图片

文章图片

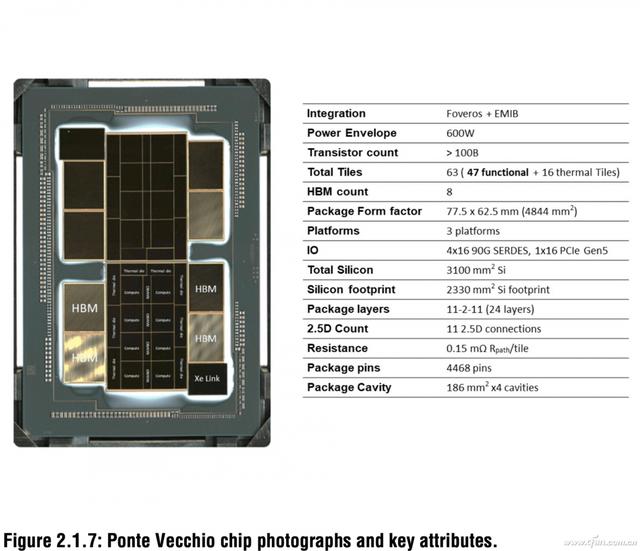

将多芯片混合封装玩到极致的 , 还要数英特尔此前发布的PonteVecchio计算加速卡 , 它使用了5种不同的制造工艺 , 内部封装多达47个芯片/单元(Tile) , 晶体管数量突破1000亿个!

文章图片

文章图片

问题来了 , 类似技术AMD也有 , 台积电和三星等代工企业也有 , 只是大家都是各自为战 , 不同工艺、功能和封装的芯片之间没有统一的通讯接口 , 造成了严重的资源浪费 。

为此 , ASE、AMD、ARM、Google云、Intel、Meta(Facebook)、微软、高通、三星、台积电十大行业巨头在3月2日联合宣布 , 将组成行业联盟 , 共同打造小芯片互连标准、推进开放生态 , 并制定了标准规范“UCIe”(UniversalChipletInterconnectExpress , 通用小芯片互连通道) , 旨在芯片封装层面确立互联互通的统一标准 。

- 如何把手机上的文档转到电脑上继续处理?

- 锐龙75700x到底值不值得入手?

- win11的配置需求提升了,你的配置还能应付吗?

- 锐龙cpu价格调整后的装机选择

- 时空猎人3最新礼包兑换码是多少(时空猎人3兑换码8月大全)

- 北京地铁:多种措施为夏日乘车再添一份清凉

- 数字服务闪耀服贸会,中关村软件园多家企业将参展

- 光与夜之恋七夕电话号码是多少(2022七夕电话号码介绍)

- 和平精英庄周梦蝶多少钱(庄周梦蝶皮肤保底价格介绍)

- 光遇七夕比翼发饰多少蜡烛(七夕比翼发饰免费获取方法)