锐龙5000系列的zen3架构评论

文章图片

文章图片

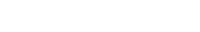

在过去的一年中 , AMD的第三代锐龙处理器可以说是好评不断 。而现在 , 它的继任者 , 锐龙5000系列处理器终于现身 。不过 , 在聊聊它们背后的Zen3架构之前 , 我们还是先列一下这次首发四款处理器的参数 。

文章图片

文章图片

首先是锐龙55600X , 作为3600X继任者的它同样是六核十二线程配置 , 基础频率3.7GHz , 加速频率高达4.6GHz 。L2缓存为3MB , L3为32MB 。默认TDP为65W 。

定位高性能游戏的锐龙75800X为八核十六线程 , 基础频率和加速频率为3.8GHz和4.7GHz 。L2是4MB , L3是32MB 。默认TDP为105W 。

文章图片

文章图片

至于代表旗舰级性能的锐龙9 , AMD这次一口气推出了两款 。分别是12核24线程的锐龙95900X和16核32线程的锐龙95950X 。两者还在频率和缓存上也有所区别 , 5900X的基础频率和加速频率为3.7GHz和4.8GHz , 拥有6MB的L2和64MB的L3 。5950X的基础频率和加速频率为3.4GHz和4.9GHz , L2和L3分别是8MB和64MB 。但默认TDP一概为105W 。

文章图片

文章图片

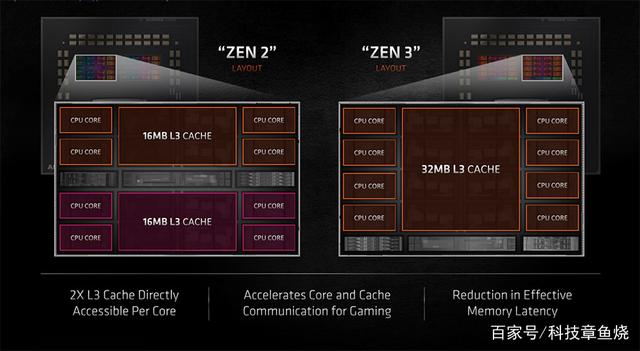

这时候 , 大家应该会注意到一件很重要的事 , 那就是除了频率外 , 锐龙5000系列的大部分配置跟上一代无异 , 甚至连制程工艺也是使用的7nm 。在看似不变的情况下 , 为什么锐龙5000系列能够有高达19%的IPC提升?这就要说到Zen3的改进了 。

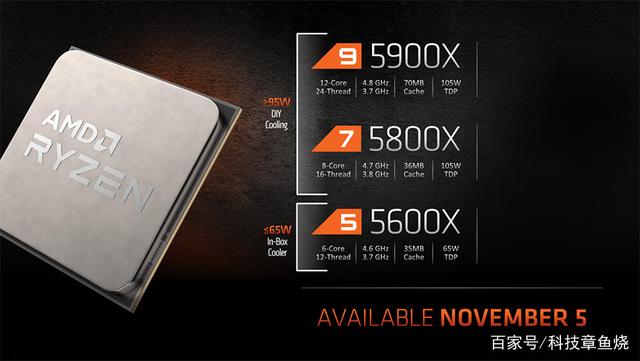

在Zen2中 , 由于IOD跟CCD的分离 , 还有IF总线的频率问题 , 通信延迟成为了一个引人关注的问题 。当时AMD的做法是加大L3缓存直到每个CCD拥有32MB的L3缓存 , 同时改进IF总线 。但受限于CCD中每个CCX仅有四核的设计 , 其实每个核心能够访问到的L3缓存只有16MB , 两个CCX靠IF总线连接在一起 。

文章图片

文章图片

而对于游戏来说 , 多线程的性能是更值得考虑的 。虽然现时的不少游戏已经做了多核优化 , 但是如即时战略、回合制战略等一大票战略游戏 , 以及部分网游 , 还是非常倚重单个核心的作用 。所以 , Zen3把CCX扩展到8核 , 即使在32MB缓存大小不变的情况下 , 每个核心能访问到的L3缓存却是翻倍的 。

文章图片

文章图片

再进一步 , 放大到多核层面的话 , 由于现在单块CCD就是CCX , 核心之间可以直接通信 , 不再存在跨CCX通信这种高延迟行为 , 所以锐龙5000系列的多核性能也是相应增强的 。这在单CCD的芯片如锐龙55600X和锐龙75800X身上会体现得特别明显 。

文章图片

文章图片

不得不说 , 仅仅是结构这一改动 , Zen3的综合性能相比Zen2就已经向前迈进一大步 。然而这还不是终点 , Zen3还从分支预测、执行引擎、缓存预取等微处理器的多个环节入手 , 并超越了业界规律 , 达成了19%IPC提升这个看似不可能的目标 。

文章图片

文章图片

- 纸嫁衣4怎么是第五部作品(纸嫁衣系列游戏介绍)

- 锐龙53600+b550主板+rx6800xt

- 希捷简系列移动硬盘的优点

- 京天amd锐龙55600x加入便是帧率大大提升的秘诀

- 联想小新air15锐龙版,职场女性必备

- 锐龙95900x+x570主板,发烧玩家的福音

- 雷柏ralemo新女性系列新春版无线键鼠,红了!

- 锐龙55600x+rx6800xt游戏主机测试

- 希捷睿翼系列移动硬盘提供1tb、4tb或5tb容量规格可选

- 北京7月查出涉嫌违法广告近5000条 这几个类别违法情况突出