这款3D-IC EDA工具或将助力中国弯道超车

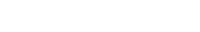

现在我们都说摩尔定律逐渐走到极限 , 作为一个经济学定律 , 摩尔定律逐渐不具备成本经济的效益 。首先高阶工艺节点已达到物理晶体管尺寸极限 , 再者随着服务器CPU和GPU裸片尺寸随时间推移不断增加 , 裸片Die尺寸不断增长已接近极限 。所以 , 业界开始考虑从不同维度出发 , 来延续摩尔定律 。

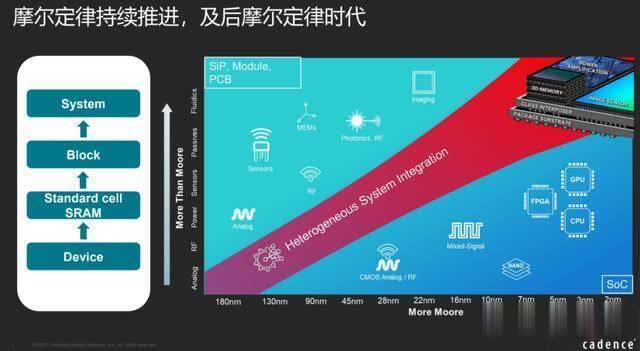

IC设计发展转向3D维度

一个芯片的组成主要分为四个层次:最底层的器件 , 标准单元库 , 片上内存SRAM , 在SRAM上会做一个芯片的Block , 再往上就是系统 。为了让摩尔定律继续往下走 , 一方面的技术努力是More Moore , 在这方面的探索主要有铝介质 , 然后是铜 , 再就是High-K , FinFET , 3纳米之后还有GAA , 靠着这些技术摩尔定律在先进工艺上不断向前发展 。

文章图片

文章图片

【这款3D-IC EDA工具或将助力中国弯道超车】但是光靠这一个维度是不足以支撑摩尔定律继续往下走的 , 因为其成本看不到显著的降低 。所以业界还在探索另外一个维度 , 就是More than Moore , 从系统角度出发 , 在封装上下功夫 , 走堆叠的路线 , 如现在的2.5D封装和3D封装等 。

下图是一张在显微镜下得到的封装图 , 在封装里面会有很大的焊球 , 这个焊球的大小影响了芯片的带宽和速度 。可以看出 , 如果一旦从2D走向3D的维度 , 其明显的好处是焊球的连线变短了 , 连线变短之后 , 功耗也会更低 , 线上的Delay减少了以后 , 芯片就会跑的比以前更快 , 得到更好的性能 。还有更加显而易见的好处是 , 因为芯片被堆叠起来 , 其封装的尺寸会小很多 。最后就是更好的良率 , 要知道 , 在流片的过程中 , 良率和面积是呈指数级关系的 , 面积越大 , 良率越低 。

文章图片

文章图片

但是3D-IC设计当前还面临着诸多挑战 , 首先是聚合和管理上的挑战 , 包括裸片的放置与Bump规划 , 而且SoC和封装团队各自为战 , 缺少代表多种技术的统一数据库;再一个挑战就是系统级验证 , 需要有跨芯片/Chiplet及封装的热分析 , 还需要系统级的裸片间的连接验证 , 3D STA签核Corner也会有“爆炸性”的增加 。而当前EDA行业的解决方案现状是脱节 , 片面 , 点工具 , 无法进行探索/缺乏早期反馈 , 导致堆叠中单个裸片的过度设计 , 成本高昂 。所有这一切都让3D STA比2D复杂度高很多 。

针对这些行业痛点和先进封装技术发展趋势 , Cadence发布了一款突破性的新产品 。

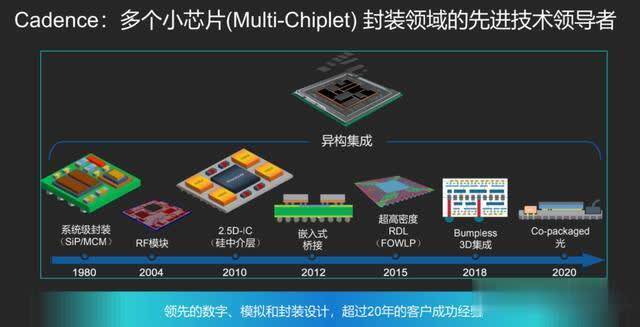

Integrity? 3D-IC 平台:由系统驱动Chiplet PPA

要说明的是 , 在先进封装领域 , 不止是封装厂和晶圆厂们厂努力的方向 , EDA软件厂商也是先进封装的重度探索者 。例如 , Cadence就已经在多个小芯片(Multi-Chiplet)封装领域耕耘了20多年 , 从1980年开始做系统级的封装 , 到2004年开始做RF模块 , 2010年开始研发2.5D技术 , 2012年开始做嵌入式的桥接 , 到现在 , 在比较流行的FOWLP、Bumpless 3D集成以及Co-package等 , 都是Cadence不断发力的方向 , 其中Co-package指的不仅是硅芯片 , Cadence甚至可以把光和硅堆叠起来 。

文章图片

文章图片

据Cadence数字与签核事业部产品工程资深群总监刘淼的介绍 , Cadence这些年正在努力转型 , 以前我们只做EDA工具 , 后来我们做了更多系统级的创新 , 最后我们希望能达到普适的智能 , 而3D-IC就是在系统创新上能够做出来的帮助客户解决当前痛点以及未来十年发展的趋势 。

- 雪里雨里,热水器照样用得起!绵阳这款系统能回收发电中产生的热量

- 昨日的镜炽阳神光皮肤制作故事中设计上结合了暖阳期待的什么的感觉创作了这款皮肤呢?(王者荣耀1月22日每日一题答案)

- 昨日的风物志推文中,有一副汉服作品是以皮肤圣诞恋歌为设计灵感的,请问这款皮肤是哪位英雄的呢(王者荣耀11月16日每日一题答案)

- 上海提升软件产业核心竞争力:重点发展EDA、CAE等工业软件

- 付完尾款隔天就到货?这款“物流机器人”好酷!

- 这款甜掉牙的爱之甜心棕是由哪对情侣带来的呢?(英雄杀08月04日每日一题答案)

- 扁鹊大大介绍的这款十全大补丸是否有成功出售呢?(英雄杀08月01日每日一题答案)

- 这款洞悉全球“风云”的卫星,121个国家和地区都在用!

- 续航长、响应快、性能好、省成本!徐工这款产品再加单

- Android手机桌面美化必备,微软出的这款工具,好看又实用