Cadence发布业界首个集成化、高容量3D

【TechWeb】11月3日消息 , 在半导体行业有一个著名的“摩尔定律” , 该定律称:当价格不变时 , 集成电路上可容纳的晶体管数目 , 约每隔18个月便会增加一倍 , 性能也将提升一倍 。而随着半导体行业的发展 , 摩尔定律开始放缓 。在这种情况下 , 为了提升芯片的性能会把Die(晶粒)做得越来越大 。但现实条件并不允许把Die做得无限大 , 而且把单个Die做大之后会导致散热不佳以及良品率低下等不可调和的问题 。针对这些问题 , 芯片设计、封装与系统的2.5D化、3D化将成为解决问题的关键 。

文章图片

文章图片

楷登电子(Cadence)近日宣布 , 正式交付全新 Cadence? Integrity? 3D-IC 平台 , 这是业界首款完整的高容量 3D-IC 平台 , 将设计规划、物理实现和系统分析统一集成于单个管理界面中 。Integrity 3D-IC 平台支持了 Cadence 第三代 3D-IC 解决方案 , 客户可以利用平台集成的热、功耗和静态时序分析功能 , 优化受系统驱动的小芯片(Chilet)的功耗、性能和面积目标(PPA) 。

文章图片

文章图片

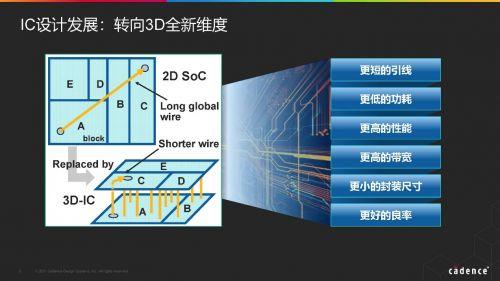

Cadence公司数字与签核事业部产品工程资深群总监刘淼介绍称:当芯片从2D世界走向3D维度的时候 , 我们会看到的一些好处 , 比如连线更短、功耗更低、性能更强 。我们从90纳米到45纳米 , 再到28纳米7纳米 , 线上的delay(延迟)会越来越多 , 线上的功耗也会越来越大 , 所以我们明显看到我们帮很多客户做5纳米 , 其中一个痛点就是要帮助他们解决线上的功耗 , 如果线短了以后 , 功耗就会更低 。线上delay减少了以后 , 芯片就会跑得比以前更快了 , 从而使芯片性能变得更强 。

文章图片

文章图片

【Cadence发布业界首个集成化、高容量3D】另外一方面就是我们可以把一个很大的芯片切成两个 , 把它堆叠起来 , 封装的尺寸会小很多 。现在封装也是一个痛点 , 很多客户拿不到产能 。不一定是晶圆厂拿不到 , 是封装拿不到 , 大的基板是很难拿到的 。所以我们一旦有了这个技术 , 就可以让他有更小的封装尺寸 。

最后是更好的良率 , 在晶圆厂流片的时候 , 良率和面积是呈指数关系的 。面积越大 , 良率越低 。所以综上所述 , 从2D走向3D我们可以看到很多好处 。

文章图片

文章图片

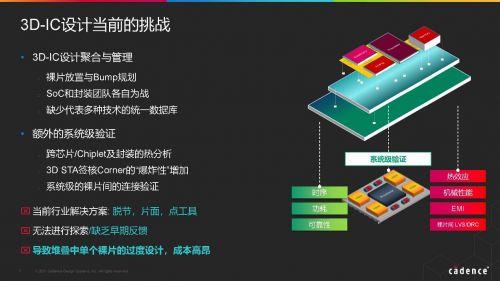

3D设计当前的挑战是什么呢?有很多 , 第一是裸片放置与Bump规划 。第二个是让一个数字工程师跟模拟工程师达成共识是很难的 , 因为他们没有共同的语言 , 共同的语言是一个统一的数据库 , 所以有聚合和管理上的挑战 。还有一个挑战是系统级验证 , 芯片的验证非常关键 。所以我们要有跨芯片/Chiplet及封装的热分析 。还有STA的签核 , STA的签核会有爆炸性的增加 。还有系统级裸片的连接验证 , 所有这一切都让3D STA比2D复杂度高很多 。

文章图片

文章图片

为了解决这些痛点 , 我们推出了一个全新的工具叫Integrity 3D-IC , 它集成了3D设计规划与物理实现 , 把所有东西放在一起 , 已经成为一个平台 。它可以做早期3D电、热、功耗和静态时序分析 。我们就要把这些东西整合起来 , 从系统上去看 。最后推出全新的3D IC平台 , 实现由系统来驱动的PPA目标 。

- 爱立信起诉苹果公司5g专利费用纠纷电信企业再次起诉

- 加强产业融合 赋能低碳发展 海尔卡奥斯智慧能源与“青碳行”签署战略合作协议

- AI技术创新、模型创新、业务创新 全新服务模式助力金融机构数字化转型

- 线上新书发布!云上带你了解有关“冬奥”的那些事儿

- 2022首场工业数字化供需对接大会举办

- 遍知教育赋能升级或将打破知识付费行业格局

- 九部门:严打平台企业超范围收集个人信息行为

- 高德联合清华发布报告:北京绿色出行意愿全国第一

- 支付宝敬业福2022怎么容易扫出来?2022敬业福福卡获取方法说明

- 少前云图计划各职业有哪些角色值得培养(少前云图计划值得培养角色推荐)